英特尔称2030年实现万亿级晶体管芯片设计,新的技术研究继续推动摩尔定律

source link: https://www.expreview.com/85865.html

Go to the source link to view the article. You can view the picture content, updated content and better typesetting reading experience. If the link is broken, please click the button below to view the snapshot at that time.

英特尔称2030年实现万亿级晶体管芯片设计,新的技术研究继续推动摩尔定律

吕嘉俭发布于 2022-12-5 16:05

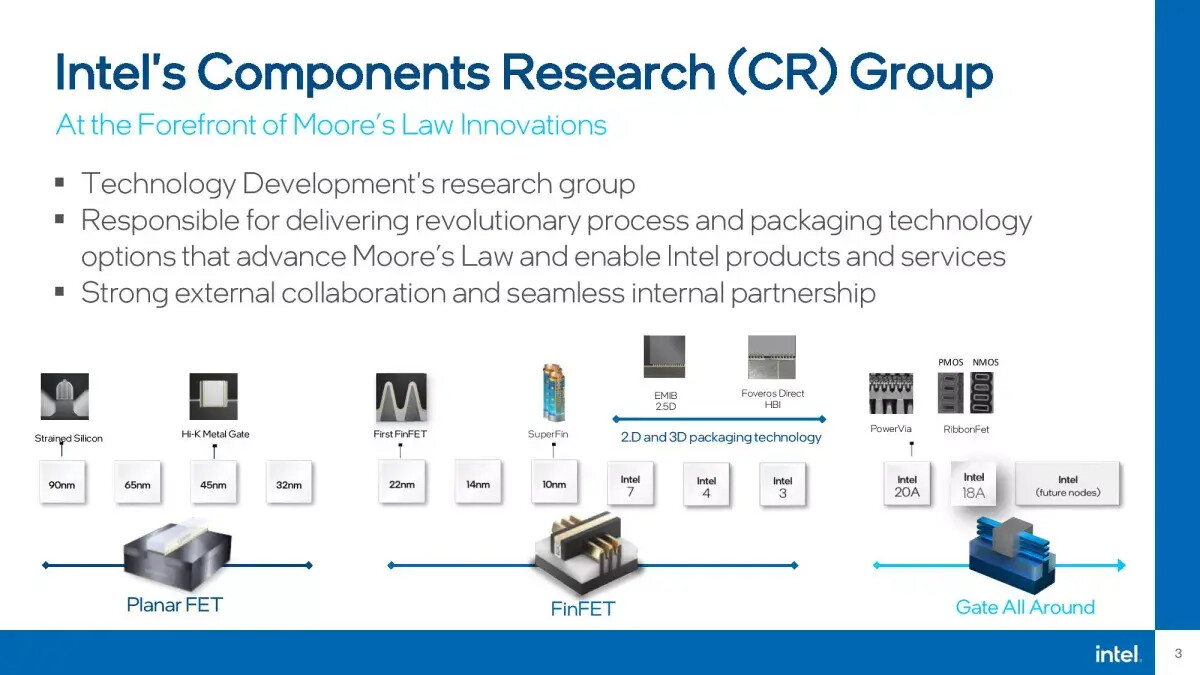

近日,英特尔在IEDM 2022上公布了最新的突破性研究,为未来芯片设计奠定了基础。其目标是将封装技术密度提高10倍,使用仅3个原子厚的新材料来推进晶体管缩放,在未来10年内实现万亿级晶体管芯片设计。

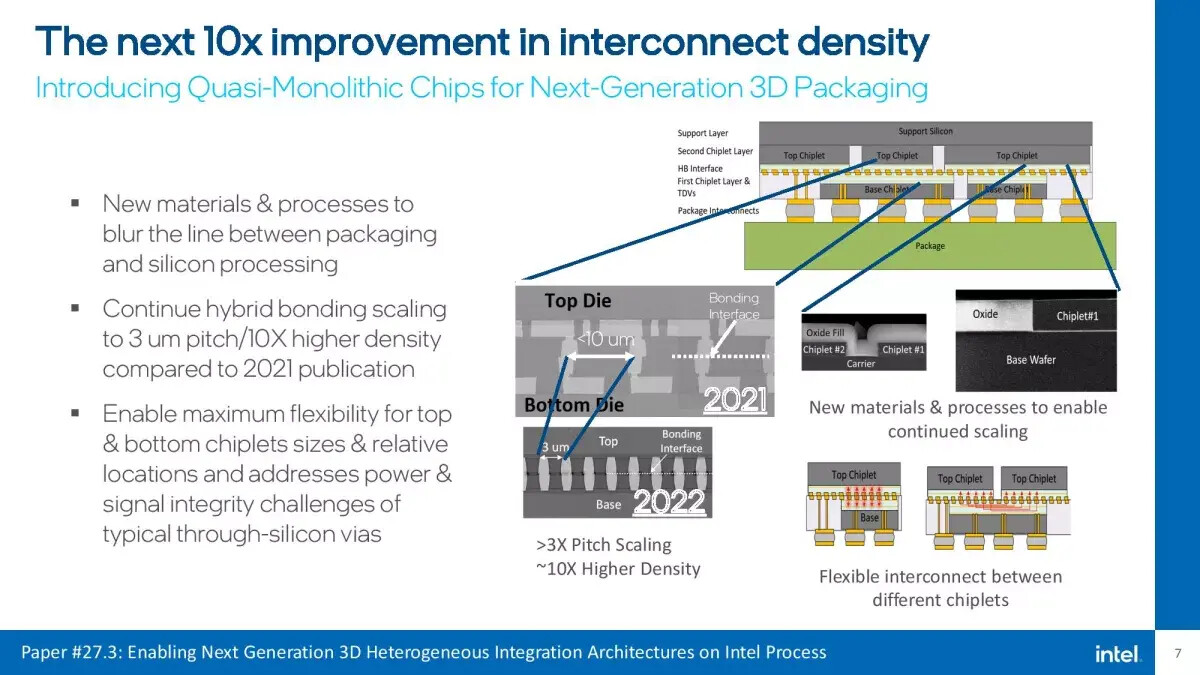

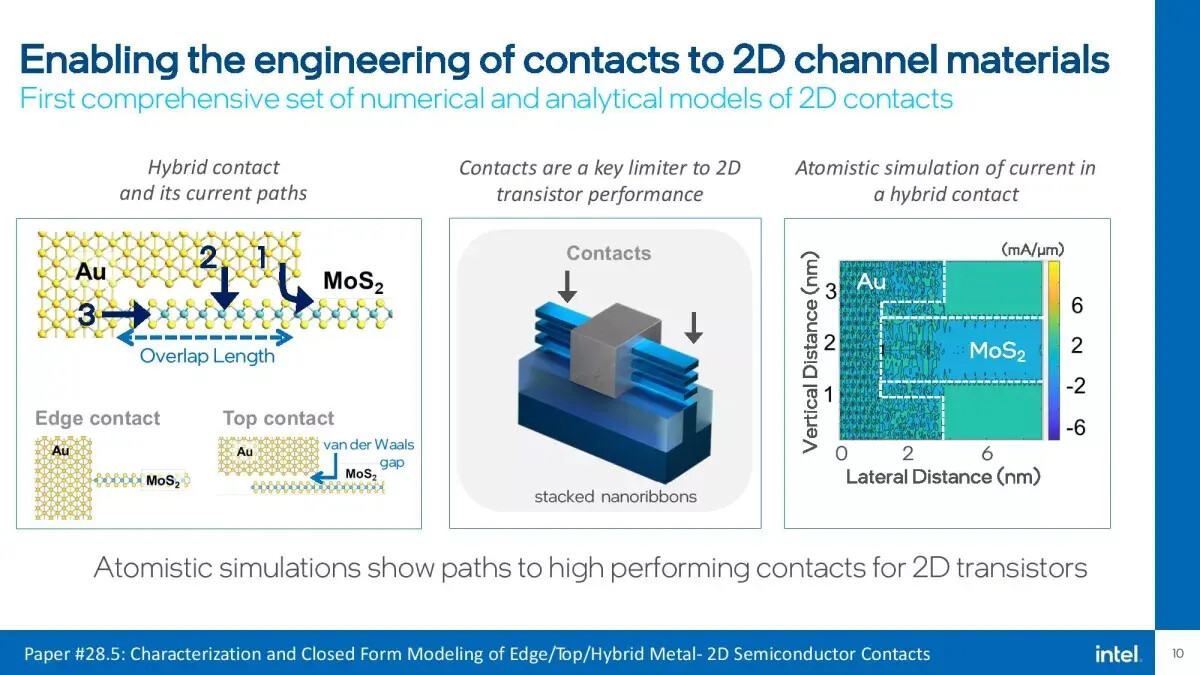

此次英特尔研究人员展示了用于晶体管的新型2D材料、将小芯片和单芯片处理器之间的性能和功耗差距缩小到几乎难以察觉的新型3D封装技术、以及可垂直堆叠在晶体管之上的全新内存等。

英特尔副总裁兼设计支持总经理Gary Patton表示:

“自晶体管发明以来的75年里,推动摩尔定律的创新继续满足世界对计算的指数级增长需求。在IEDM 2022上,英特尔展示了突破当前和未来障碍、满足这一永不满足的需求以及在未来几年保持摩尔定律活力所需的前瞻性和具体研究进展。”

英特尔表示,基于hybrid bonding的下一代3D封装技术可以将集成密度提高10倍,同时间距缩小到3微米,使得多芯片互联可媲美目前的单芯片设计;使用仅3个原子厚的2D新材料,在常温下以低漏电流实现了双栅结构上晶体管近乎理想的开关,同时可在单芯片上装入更多的晶体管,进一步为高性能和可扩展的晶体管通道铺平了道路;可垂直堆叠在晶体管之上的全新内存及堆叠铁电电容,性能媲美传统铁电沟道电容,可用于在逻辑芯片上打造FeRAM。

Recommend

About Joyk

Aggregate valuable and interesting links.

Joyk means Joy of geeK