DDR5 vs DDR4:I3C和I2C相较提高了什么?为什么必须升级到I3C?

source link: https://zhuanlan.zhihu.com/p/421387137

Go to the source link to view the article. You can view the picture content, updated content and better typesetting reading experience. If the link is broken, please click the button below to view the snapshot at that time.

DDR5 vs DDR4:I3C和I2C相较提高了什么?为什么必须升级到I3C?

在上一篇文章中:

我提到在DDR5中SPD的一个显著的改变是升级为SPD Hub,也就是它还作为I3C的Hub存在。有些同学对此不太理解,今天我们就来看看DDR5中的I3C的连接,并一起讨论一下为什么DDR5有需求要升级到I3C了。在此之前,大家可以预习一下什么是I3C:

I3C in DDR5

上个月MIPI组织的MIPI DevCon 2021[1]因疫情的原因在线上举行,作为DDR5和I3C的主要贡献者之一的Intel,派出Azusena Lupercio, Juan Orozco, Nestor Hernandez在会上做了“DDR5 服务器平台解决方案内的 I3C 信号完整性挑战 ”主题演讲。其中的不少内容颇为精彩,这里借花献佛将其中关于I3C的连接方式图片分享给广大读者,其他信号完整性的内容也十分有趣,有兴趣的读者可以自行在参考资料1中寻找。

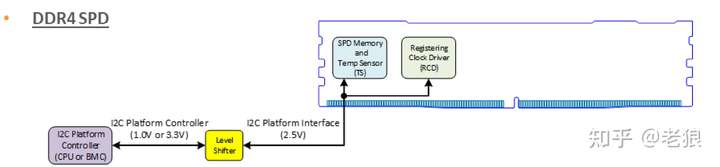

在DDR4中,每个DIMM上,有两个设备连接在I2C总线上:

I2C in DDR4

I2C in DDR4分别是是DIMM的温度传感器和RDIMM的RCD(什么是RCD可以参考我以前的RDIMM文章)。I2C的频率一般在100KHz 至 1MHz之间,普通情况下是400KHz。较慢的传输速度在这种情况下还不凸显,但DDR5的到来让情况发生了变化。

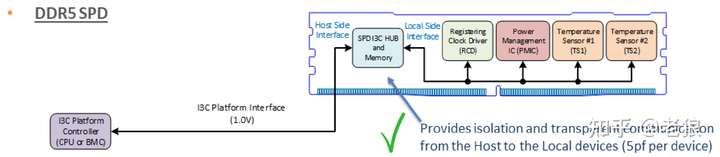

I3C in DDR5

I3C in DDR5在DDR5 DIMM中,一般有5个I3C从设备:SPD、RCD、PMIC、TS1和TS2。这让一个SPD链中IxC的从设备从16个变成了40个,大大增加了负担。这就需要I3C的高速上场了,I3C的频率可达到12.5MHz,相较I2C提升了12.5 倍至 125 倍。大大加速了启动速度,尤其是服务器BIOS的启动速度(想想为什么是服务器)。

SPD升级成SPD HUB的主要原因也在图片中展现了。DDR4使用的I2C的电压是2.5V,而CPU的Power Rail普遍是1.0V或者3.3V,需要电平转换。2.5V的总线耗电也相当高。而DDR5中,使用的是I3C,它在设计时候就考虑了省电,电压是1.0V,和CPU的电压相容。同时,SPD芯片带有I3C HUB的功能,也就是它作为一个I3C的设备和CPU相连,其他四个I3C设备作为从设备连在它下面。这样主板就不需要电平转换电路了,同时SPD HUB还让CPU和DIMM做了电子隔离,CPU只看到一个负载,降低了I3C信号完整性调教的难度。但另一方面,SPD HUB这个二传手,会让单向传输增加了6ns的延迟,来回就是增加了12ns的延迟。

好了,I3C的内容应该已经足够清楚了。下一节,我们来看看DDR5中,内存修复功能(Post-package repair,PPR)中软修复sPPR(Soft PPR)和硬修复(Hard PPR),分别作了那些提高。

最后推荐一款内存:

其他内存相关文章:

欢迎大家关注本专栏和用微信扫描下方二维码加入微信公众号"UEFIBlog",在那里有最新的文章。关注公众号,留言“资料”,有一些公开芯片资料供下载。

Recommend

About Joyk

Aggregate valuable and interesting links.

Joyk means Joy of geeK