IMEC公布亚1nm晶体管路线图:3D堆叠的CMOS 2.0计划 - 超能网

source link: http://www.expreview.com/88552.html

Go to the source link to view the article. You can view the picture content, updated content and better typesetting reading experience. If the link is broken, please click the button below to view the snapshot at that time.

IMEC公布亚1nm晶体管路线图3D堆叠的CMOS 2.0计划

吕嘉俭发布于 2023-5-29 11:33

本文约 730 字、3 张图表,需 2 分钟阅读

IMEC成立于1984年,目前是欧洲领先的独立研究中心,研究方向主要集中在微电子,纳米技术,辅助设计方法,以及信息通讯系统技术(ICT)。近日,IMEC就发布了其1nm以下工艺的路线图,分享了对应的晶体管架构研究和开发计划。

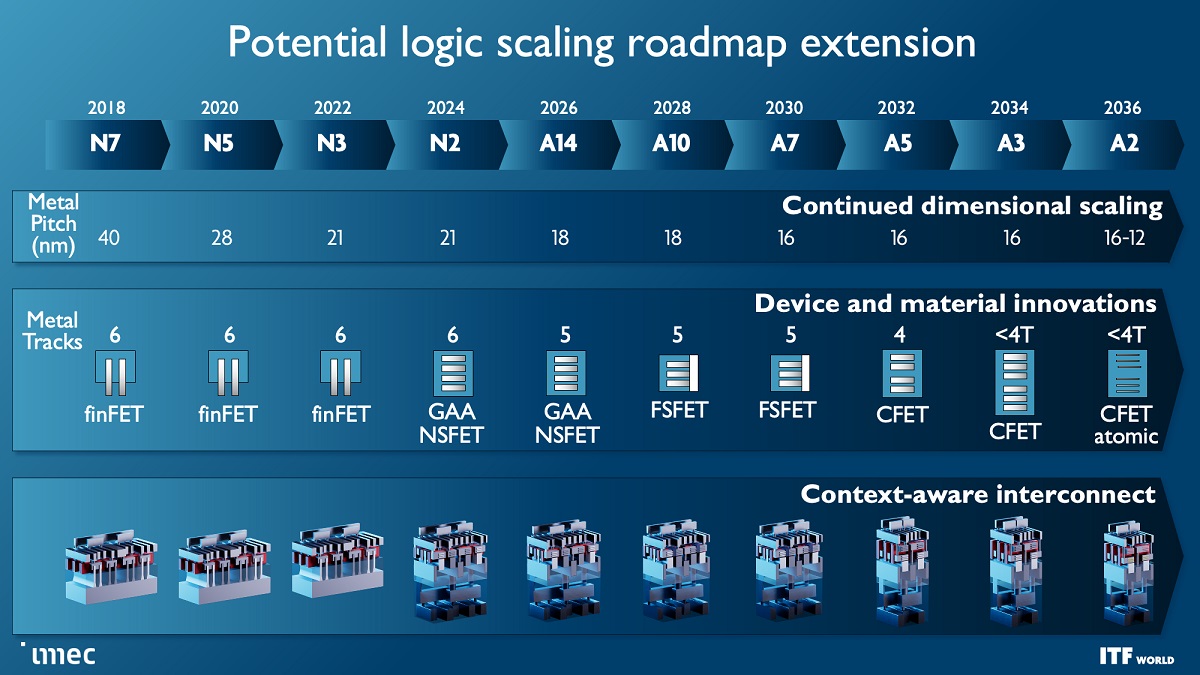

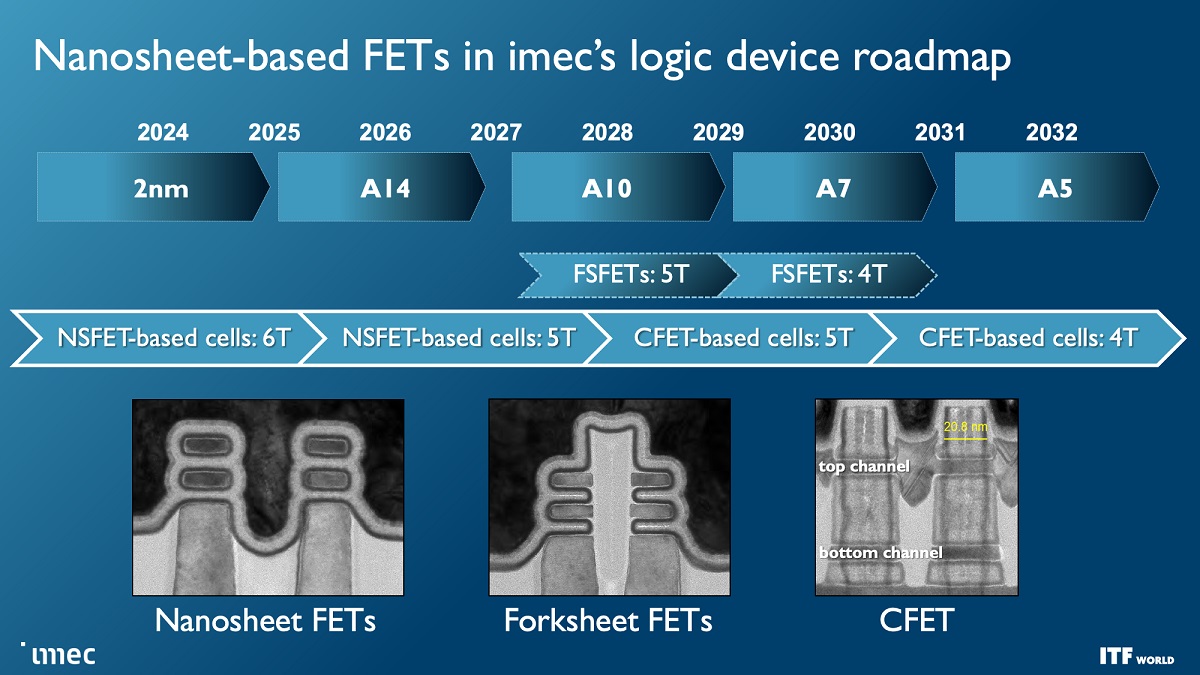

据TomsHardware报道,IMEC的工艺路线图显示,FinFET晶体管将在3nm走到尽头,然后过渡到新的Gate All Around(GAA),预计2024年进入大批量生产,之后还会有FSFET和CFET等。A代表的是埃米,10A等于1nm。

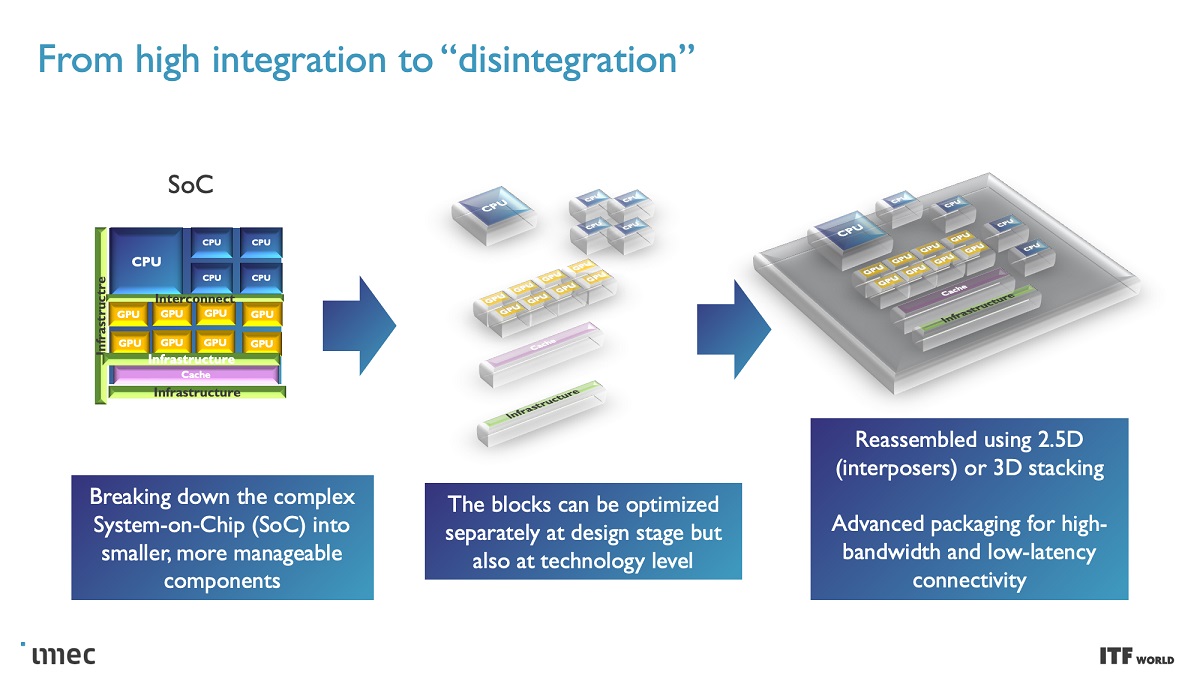

随着时间的推移,迁移到更小的制程节点会变得越来越昂贵,原有的单芯片设计方法已经让位给小芯片设计,意思是将芯片的各种功能分解成各种小芯片,然后再连接到一起作为整体运行。IMEC对CMOS 2.0范式的愿景包括将芯片分解成更小的部分,将缓存和存储器分成具有不同晶体管的单元,然后以3D排列堆叠在其他芯片功能之上。这种方法还将严重依赖后端供电网络(BPDN),会将所有供电改到晶体管的背面。

通过系统技术协同优化(STCO)重新思考设计过程,对系统和目标应用的需求进行建模,然后利用这些知识为创建芯片的设计决策提供信息。在这个过程中,会将芯片拆分为单独单元,以使用不同类型的晶体管来优化每个单元所需的性能特征,从而降低成本。其目标之一是将缓存/内存拆分到它们自己独特的3D堆叠设计层,从而降低芯片堆栈的复杂性。

CMOS 2.0是通往真正3D芯片的道路,目前AMD利用3D V-Cache技术将L3缓存堆叠在计算芯片顶部以增大容量,IMEC设想的是整个缓存层次包含在自己的层中,L1、L2和L3缓存垂直堆叠在构成处理核心的晶体管之上。每一层缓存都将用最适合该任务的晶体管来创建,由于SRAM的缩放已大幅减缓,这意味着可以让SRAM有可能使用旧的制程节点来降低成本,理想情况下3D堆叠还可以帮助缓解与大型缓存相关的延迟问题。

Recommend

About Joyk

Aggregate valuable and interesting links.

Joyk means Joy of geeK