了解SPI总线常识,竟如此简单

source link: https://www.eefocus.com/communication/526433

Go to the source link to view the article. You can view the picture content, updated content and better typesetting reading experience. If the link is broken, please click the button below to view the snapshot at that time.

1、SPI简介

SPI,即Serial Peripheral Interface的英文缩写。从字面意思看就是串行外部设备接口,是一种全双工、高速、同步的通信总线。

SPI最早是摩托罗拉公司开发的全双工同步串行总线,用于微控制器(MCU)连接外部设备之间的同步串行通信。主要应用于Flash、数模转换器、信号处理器、控制器、EEPROM存储器等外设中。

SPI总线属于一主多从接口,和I2C不同的是,SPI 采用CS片选来控制主机与那个从机通信。

现在的单片机几乎都支持SPI总线,其已经成为一种高速、同步、双工的通用标准,在IoT产品中得到广泛应用。

2、SPI 有几根线?

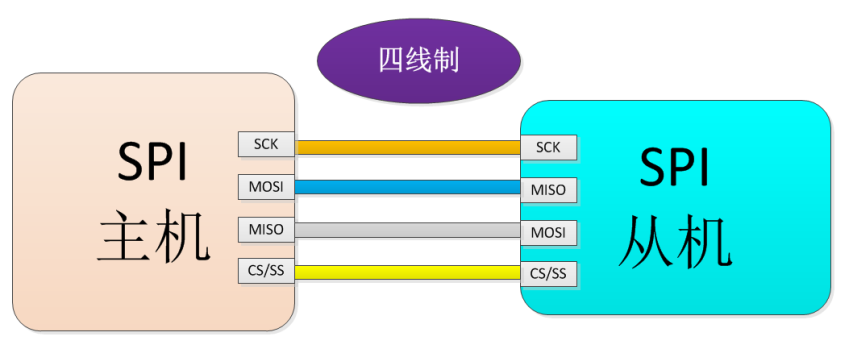

SPI通常有4根线(四线制),可实现全双工通信。

【SCK】: 串行时钟(Serial Clock)

【MOSI】:主发从收信号(Master Output, Slave Input)

【MISO】:主收从发信号(Master Input, Slave Output)

【CS/CS】:片选信号(Slave Select)

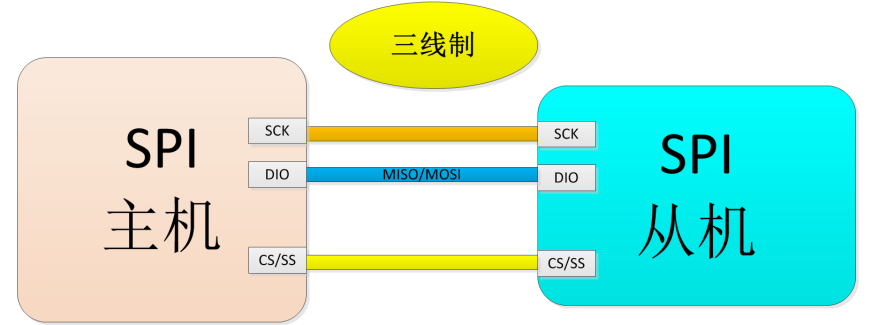

SPI应用也有3根线(三线制),实现半双工通信。

3、SPI 通信原理

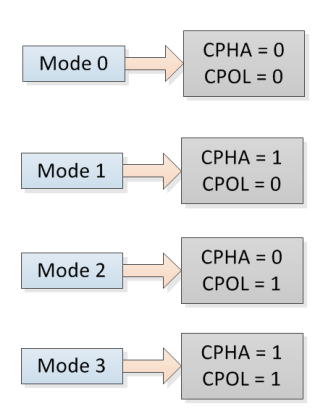

SPI模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,通过CPHA(时钟相位)、CPOL(时钟极性)来控制设备的通信模式。

时钟极性CPOL是用来配置SCK的电平在哪种状态时是有效状态或者空闲状态。时钟相位CPHA是用来配置数据采样是在哪个边沿:

CPHA=0,数据采样是在第1个边沿,数据发送在第2个边沿

CPHA=1,数据采样是在第2个边沿,数据发送在第1个边沿

CPOL=0,当SCLK=0时处于空闲态,有效状态就是SCLK处于高电平时

CPOL=1,当SCLK=1时处于空闲态,有效状态就是SCLK处于低电平时

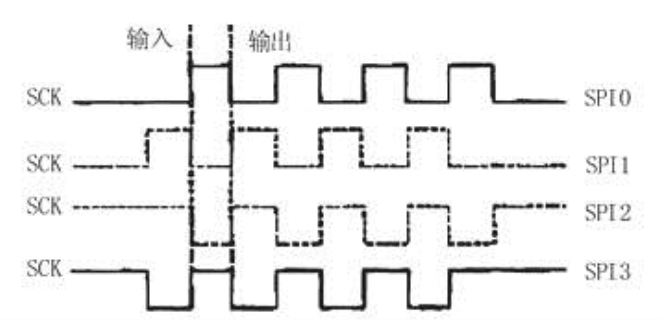

CPHA=0、CPOL=0:此时空闲态时,SCK处于低电平,数据采样是在第1个边沿,就是SCK由低电平到高电平的跳变,所以数据采样是在上升沿(准备数据),(发送数据)数据发送是在下降沿。

CPHA=0、CPOL=1:此时空闲态时,SCK处于高电平,数据采集是在第1个边沿,即SCK由高电平到低电平的跳变,所以数据采集是在下降沿,数据发送是在上升沿。

CPHA=1、CPOL=0:此时空闲态时,SCK处于低电平,数据发送是在第1个边沿,即SCK由低电平到高电平的跳变,所以数据采样是在下降沿,数据发送是在上升沿。

CPHA=1、CPOL=1:此时空闲态时,SCK处于高电平,数据发送是在第1个边沿,即SCK由高电平到低电平的跳变,所以数据采集是在上升沿,数据发送是在下降沿。

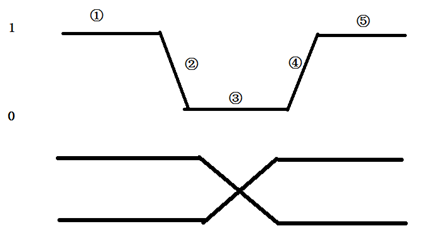

另外,分享个时序图识图方法。交叉线:数据允许发生改变,但不一定要变。平行线:数据不允许发生改变,必须稳定发送。

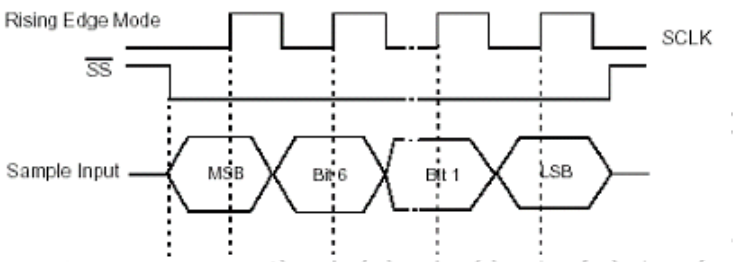

再细说传输时序。SPI接口在内部硬件实际上是两个简单的移位寄存器,传输的数据为8位,在主器件产生的从器件使能信号和移位脉冲下,按位传输,高位在前,低位在后。如下图所示,在SCLK的下降沿上数据改变,上升沿一位数据被存入移位寄存器。SPI接口没有指定的流控制,没有应答机制确认是否接收到数据。

4、SPI 的特征

4.1 优势

- 主从及通信模式

4.2 缺点

- 无指定流控制

- 没有应答机制确认

版权声明:与非网经原作者授权转载,版权属于原作者。文章观点仅代表作者本人,不代表与非网立场。文章及其配图仅供工程师学习之用,如有侵权或者其他问题,请联系本站作侵删。 侵权投诉

Recommend

About Joyk

Aggregate valuable and interesting links.

Joyk means Joy of geeK