TSMC台积电将推出5个版本的3nm技术,并用FinFlex提高设计灵活性

source link: https://www.eefocus.com/component/520454

Go to the source link to view the article. You can view the picture content, updated content and better typesetting reading experience. If the link is broken, please click the button below to view the snapshot at that time.

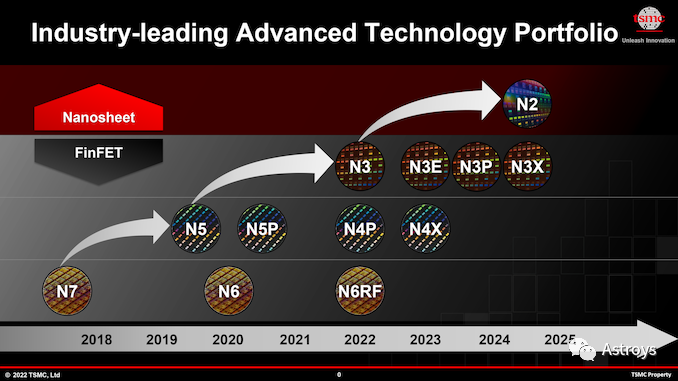

TSMC上周四进行了2022年TSMC技术研讨会,按照惯例分享了其工艺技术路线图及未来的扩张计划。TSMC这次宣布的关键事项之一是N3(3nm级)和N2(2nm级)系列的前沿节点,这些节点将在未来几年用于制造先进的CPU、GPU和SoC。

N3:未来三年5个节点

随着制造工艺越来越复杂,它们的寻路和研发时间也被拉长了,所以我们不再看到TSMC和其他代工厂每两年推出一个全新的节点。对于N3,台积电的新节点推出周期将延长到了2.5年左右,而N2将延长到3年左右。

这意味着TSMC需要提供N3的增强版,以满足其客户的需求,这些客户仍在寻求每瓦性能的提升,以及每一年左右的晶体管密度的提升。TSMC及其客户需要多版本的N3的另一个原因是,N2依赖于基于nanosheet技术的全新的GAA FET(gate-all-around field-effect transistors),预计这将带来更高的成本、新的设计方法、新的IP和许多其他变化。虽然前沿芯片的开发者会迅速跳到N2,但TSMC的许多普通客户将在未来几年内坚持使用各种N3技术。

在2022年的TSMC技术研讨会上,谈到了四种N3衍生出的制造工艺(共5个3nm级节点),N3E、N3P、N3S和N3X将在未来几年内推出。这些N3衍生版预计将为超高性能应用提供更好的工艺窗口、更高的性能、更高的晶体管密度和更大的电压。所有这些技术都将支持FinFlex,这是TSMC的一个“秘诀”,大大增强了其设计灵活性,使芯片设计者能够精确地优化性能、功耗和成本。

请注意,TSMC在2020年左右才开始分别公布模拟、逻辑和SRAM的晶体管密度提升情况。一些数字仍然反映了由50%逻辑、30%SRAM和20%模拟组成的“混合”密度。

N3和N3E:即将量产

TSMC的第一个3nm级节点是N3,这个节点有望在今年下半年开始量产。这项技术主要针对早期采用者(Apple等公司),他们可以投资于前沿设计,并将受益于前沿节点所提供的PPA(performance, power, area)优势。但由于它是为特定类型的应用定制的,N3的工艺窗口(产生确定结果的参数范围)相对较窄,就产量而言,它可能不适合所有的应用。

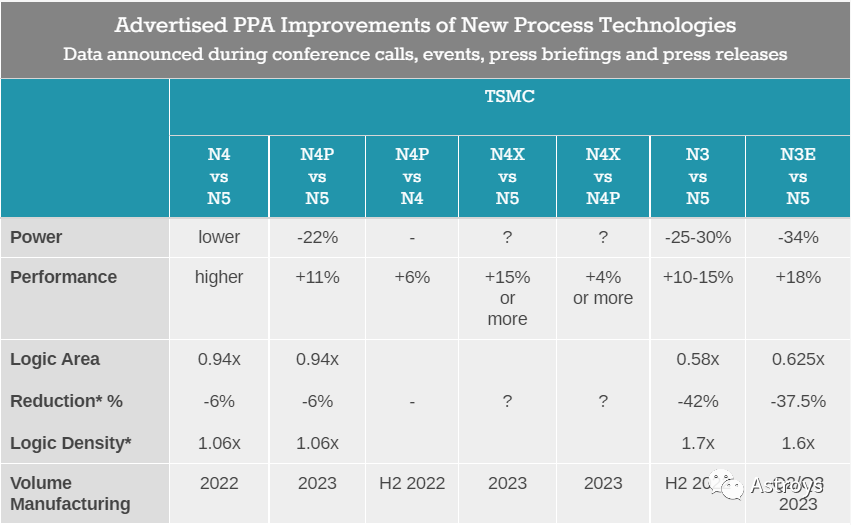

这就是N3E发挥作用的时候了。这项新技术提高了性能,降低了功耗,并增加了工艺窗口,从而提高了产量。但代价是,该节点的逻辑密度略有下降。与N5相比,N3E功耗低34%(在相同的速度和复杂度下)或性能提高18%(在相同的功耗和复杂度下),并将逻辑晶体管密度提高了1.6倍。

值得注意的是,根据TSMC的数据,N3E将提供甚至比N4X(2023年)更高的时钟速度。然而,后者还将支持1.2V以上的超高驱动电流和电压,届时它将能够提供无与伦比的性能,但功耗非常高。

总的来说,N3E看起来是一个比N3更通用的节点,这就是为什么TSMC在这一点上的3nm的衍生版比它的5nm级节点在类似的发展阶段更多的原因,这并不奇怪。

使用N3E的芯片的风险量产将在未来几周开始(即2022年第二季度或第三季度),量产将在2023年中期开始。因此,预计商用N3E芯片将在2023年底或2024年初上市。

N3P、N3S和N3X:性能、密度、电压

N3的改进并不局限于N3E。TSMC将在2024年左右推出N3P,即其制造工艺的性能增强版,以及N3S,即该节点的密度增强版。可惜TSMC目前没有披露这些衍生版与基线N3相比会有哪些改进。事实上,在这一点上,TSMC甚至没有在其路线图的所有版本中显示N3S,所以试图猜测它的特性真的不合适。

最后,对于那些无论功耗和成本都需要超高性能的客户,TSMC将提供N3X,这基本上是N4X理论的继承者。同样,TSMC没有透露这个节点的细节,只是说它将支持高驱动电流和电压。我们可能会猜测N4X可能使用背面供电,但由于我们谈论的是基于FinFET的节点,而TSMC只打算在基于nanosheet的N2中实现背面供电轨道,我们不确定是否如此。尽管如此,TSMC在提高电压和增强性能方面可能有许多王牌。

FinFlex: N3的秘诀

说到增强功能,我们肯定应该提到TSMC为N3设计的秘诀:FinFlex技术。简而言之,FinFlex允许芯片设计者精确地定制他们的构建模块,以实现更高的性能、更高的密度和更低的功耗。

当使用基于FinFET的节点时,芯片设计者可以选择使用不同晶体管的不同库。当开发者需要以性能为代价最小化芯片尺寸并节省功耗时,他们会使用double-gate single-fin(2-1)FinFET。但是,当他们需要在芯片尺寸和更高功耗的权衡下最大限度地提高性能时,他们使用triple-gate dual-fin(3-2)FinFET。当开发者需要一个平衡点时,他们会使用dual-gate dual-fin(2-2)FinFET。

目前,在整个芯片或SoC设计的整个模块中,芯片设计师必须坚持使用一种库/晶体管类型。例如,CPU内核可以使用3-2 FinFET来实现,以使其运行速度更快,或者使用2-1 FinFET来降低其功耗和占用空间。这是一个公平的权衡,但它不是所有情况下的理想选择,特别是当我们在谈论3nm级节点时,其使用成本将比现有技术更高。

对于N3,TSMC的FinFlex技术将允许芯片设计者在一个区块内混合和匹配不同种类的FinFET,以精确定制性能、功耗和面积。对于像CPU内核这样的复杂结构,这样的优化给了很多机会来提高内核性能,同时还能优化芯片尺寸。因此,我们渴望看到SoC设计者在迫在眉睫的N3时代如何利用FinFlex的优势。

FinFlex不能替代节点专业化(性能、密度、电压),因为工艺技术比相同工艺技术中的库或晶体管结构有更大的差异,但FinFlex看起来是优化TSMC N3节点的性能、功率和成本的一个好方法。最终,这项技术将使FinFET的灵活性更接近基于nanosheet的GAAFETs,后者将提供可调节的通道宽度以获得更高的性能或降低功耗。

与TSMC的N7和N5一样,N3将是TSMC另一个长期节点系列。特别是随着TSMC 2nm级的基于nanosheet的GAAFet的飞跃,3nm系列将是该公司“经典”前沿FinFET节点的最后一个系列,也是很多客户将坚持数年(或更长时间)的节点。这也是为什么TSMC正在为不同的应用准备多个版本的N3,以及FinFlex技术,为芯片设计者提供一些额外的设计灵活性。

首批N3芯片将在未来几个月内投入生产,并在2023年初投放市场。同时,TSMC在2025年推出N2工艺技术后,还将继续使用其N3节点。

[参考文章]

TSMC Readies Five 3nm Process Technologies, Adds FinFlex For Design Flexibility — Anton Shilov

版权声明:与非网经原作者授权转载,版权属于原作者。文章观点仅代表作者本人,不代表与非网立场。文章及其配图仅供工程师学习之用,如有侵权或者其他问题,请联系本站作侵删。 侵权投诉

Recommend

About Joyk

Aggregate valuable and interesting links.

Joyk means Joy of geeK