Hot Chips 33大会:AMD展示3D芯片封装技术,IBM发布7纳米Telum处理器-InfoQ

source link: https://www.infoq.cn/news/aVGYpD7ldM6vEpErNVR0

Go to the source link to view the article. You can view the picture content, updated content and better typesetting reading experience. If the link is broken, please click the button below to view the snapshot at that time.

Hot Chips 33 大会:AMD 展示 3D 芯片封装技术,IBM 发布 7 纳米 Telum 处理器

2021 年 8 月 25 日

美国时间 8 月 22 日,为期 3 天的 Hot Chips 33 芯片大会正式召开。受新冠疫情影响,本次会议在线上播出,付费注册才能收看。

本月早些时候,Hot Chips 官方公布了大会日程,从日程中可以看到,Intel、AMD、NVIDIA、IBM、台积电等芯片巨头都将登场,讲解各家的最新芯片架构、封装技术等。

AMD 展示 3D 芯片封装技术

据外媒报道,在 Hot Chips 33 芯片大会上,AMD 进一步展示了堆叠技术。

事实上,在 6 月初的 Computex 大会上,AMD 就曾公布过 3D V-Cache 技术的部分细节。

AMD 在 Computex 上展示的 3D V-Cache 是在锐龙 9 5900X 上简单地增加了一个额外的 L3 缓存。3D 堆叠排列使 AMD 能够使用一种制造工艺,该工艺允许它的每一个计算芯片上都堆叠了 64MB SRAM,可作为额外的三级缓存使用,这样加上处理器原本集成的 64MB,总的三级缓存容量就达到了 192MB。对比标准的锐龙 9 5900X 处理器,频率都固定在 4GHz,3D V-Cache 缓存加入之后,游戏性能平均提升了多达 15%。

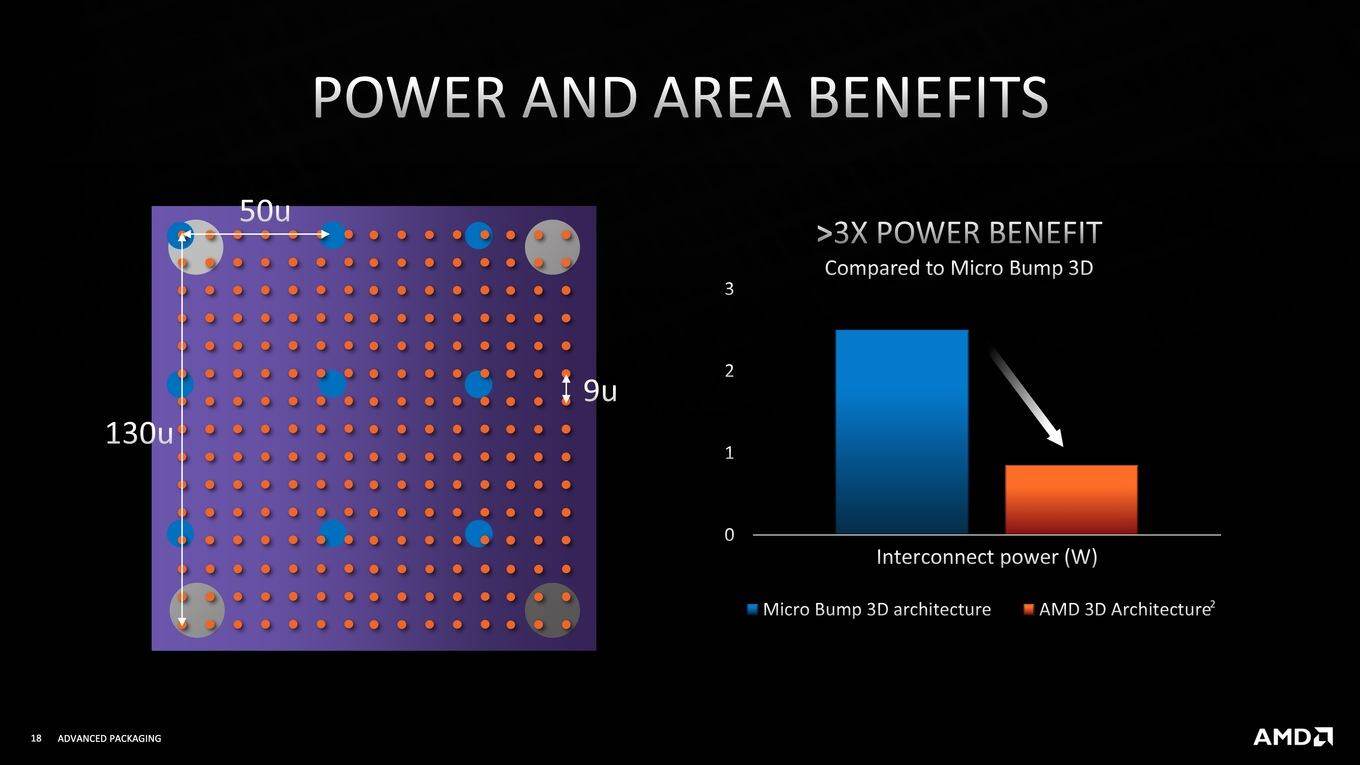

在 Hot Chips 33 上,AMD 透露了有关 3D V-Cache 的更多细节。根据介绍,AMD 实现了 3D V-Cache 的 TSV 之间的距离仅为 9 μm。

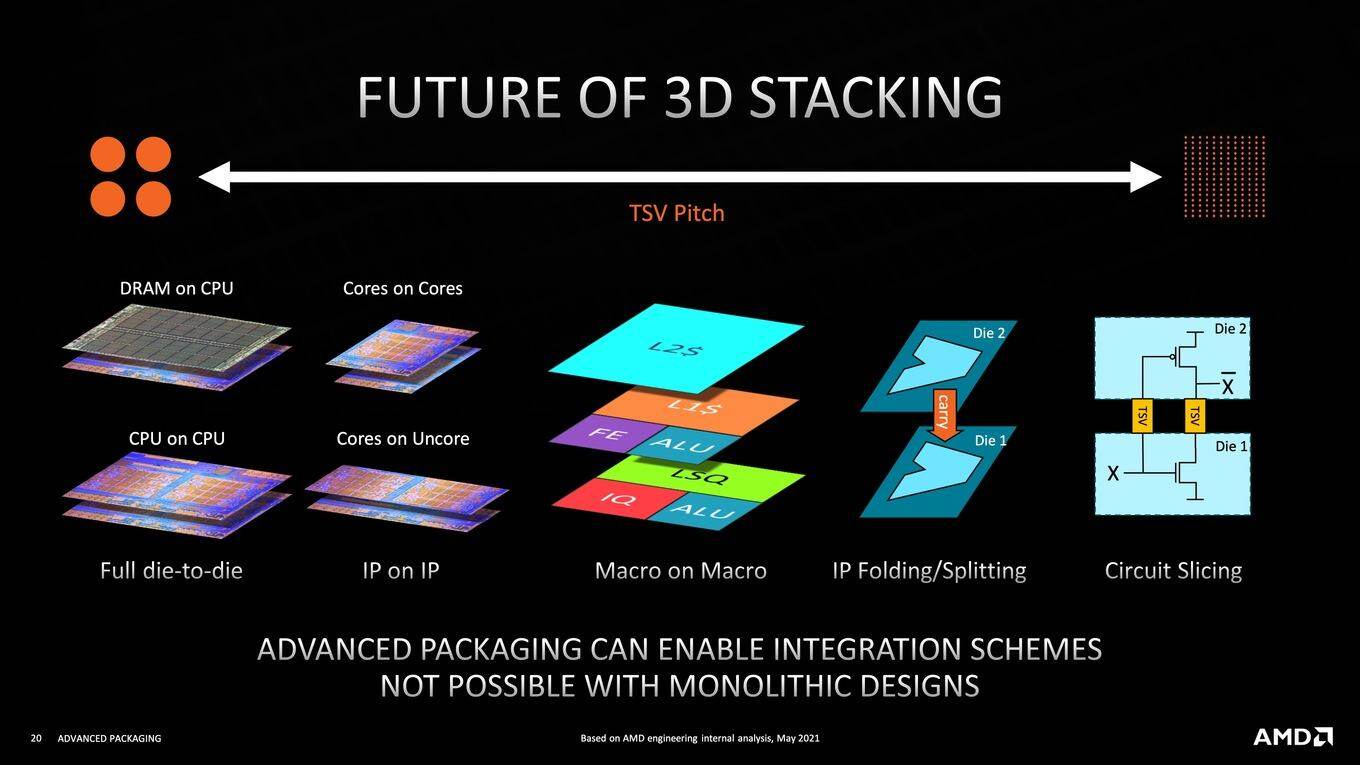

此外,3D V-Cache 只是 AMD 3D 堆栈计划的第一步。在下一步中,AMD 正在考虑将单个内核置于彼此之上,就像内核可以堆叠在处理器的非内核区域一样。

AMD 封装高级研究员 Raja Swaminathan 表示,并非每个解决方案都适合所有产品。但是,未来无疑属于模块化设计与匹配协调封装,以延续摩尔定律。业界对此已达成共识,知名厂商提供的各种解决方案就是明证。

IBM 发布 Telum 处理器,主打 AI 加速

在 Hot Chips 33 芯片大会上, IBM 公布了下一代 Z 系列企业级处理器 Telum。

据 IBM 介绍,Telum 采用三星 7nm 工艺制造,面积 530 平方毫米,集成多达 225 亿个晶体管,拥有全新的分支预测、缓存、多芯片一致性互连,性能提升超过 40%。

此外,Telum 还是 IBM 第一款结合 AI 加速推论功能的处理器芯片,其单芯片性能超过 6TFlops,内部矩阵阵列拥有 128 个单元,延迟超低且一致,支持 ML、RNN、CNN 各种模型,支持企业级内存虚拟化和保护,可通过硬件、固件更新进行拓展。

Telum 可用于 AI 或深度学习模型推论。IBM 表示,金融企业可以将训练完的 AI 或深度学习模型打包到采用 Telum 处理器的 IBM 系统上来部署与进行 AI 推论。

另据了解,首款采用 Telum 处理器的 IBM 系统预计于 2022 年上半年推出。

Recommend

About Joyk

Aggregate valuable and interesting links.

Joyk means Joy of geeK