IME突破四层3D堆叠技术,未来芯片或许就像三明治

source link: https://www.expreview.com/79773.html

Go to the source link to view the article. You can view the picture content, updated content and better typesetting reading experience. If the link is broken, please click the button below to view the snapshot at that time.

IME突破四层3D堆叠技术,未来芯片或许就像三明治

吕嘉俭发布于 2021-7-20 12:22

随着半导体工艺技术的研发愈加困难,想突破更先进的工艺变得相当不容易。且不说英特尔在14nm工艺节点徘徊了很久,想进入10nm以下区域估计也要费不少周折,即便处于领先地位的台积电(TSMC),近期也传出3nm工艺延期的消息,至于台积电身后的追随者三星,似乎也不是特别顺利。

既然工艺技术提升受阻,或者要换个方式来提高未来芯片的性能了,也许3D堆叠技术是一种选择。据TomsHardware报道,Institute of Microeletronics(IME)的研究人员刚刚实现了一项技术突破,实现了多达四个半导体层的堆叠。与传统的二维制造技术相比,可以节省50%的成本,该技术可能会用于未来的CPU和GPU上,或许真正的新一代3D芯片堆叠就在眼前。

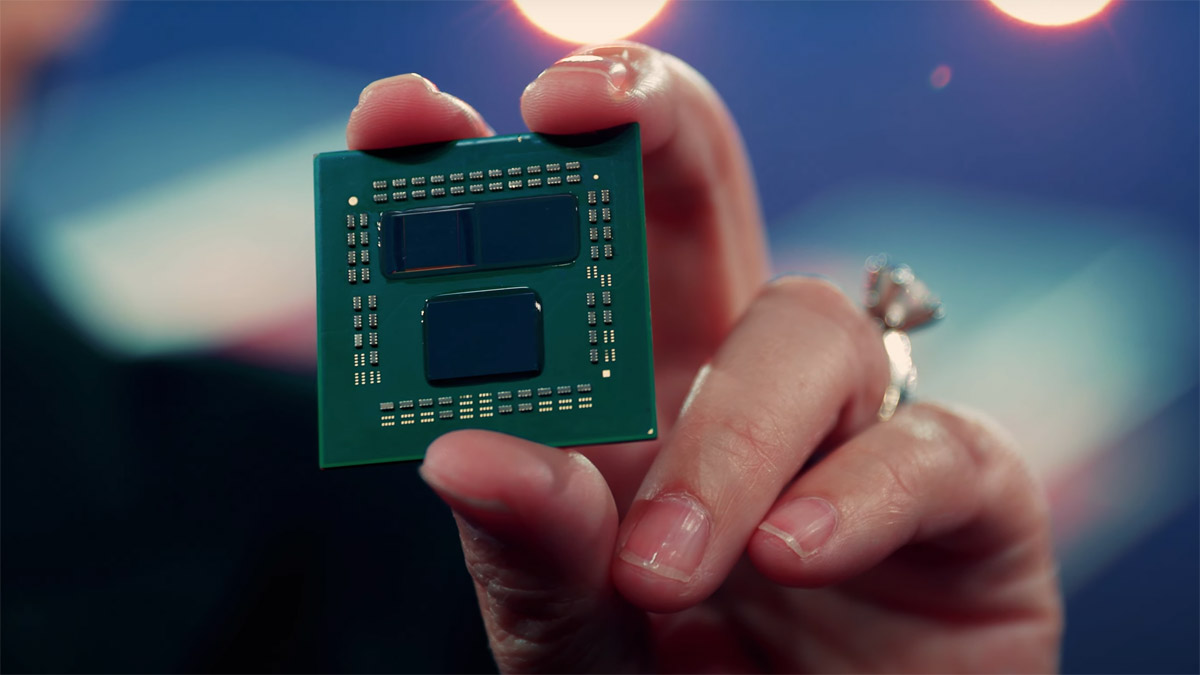

相比此前台积电和AMD的SRAM堆叠技术,IME的这项新技术更进一步。在AMD展示采用3D堆叠技术的Ryzen9 5900X处理器的原型设计里,基于台积电无损芯片堆叠技术的产品只有两层,第一层是Zen 3架构的CCX,第二层是96MB的SRAM缓存。IME的研究人员则展示了另外一种工艺,通过TSV(硅通孔技术)成功粘合了四个独立的硅层,允许不同模具之间通信。

这样的技术带来的好处是显而易见的,可以允许芯片由不同工艺的组件在不同晶圆中制造,在近期英特尔的演讲中可以感觉到,新芯片的设计上已经往这方面的思路发展了。这样的堆叠当然也会带来其他的问题,就如许多人所想的那样,虽然芯片效率提高了,但要面对散热问题,所以会看到许多奇特的、直接用在芯片上的散热技术开始浮现。

Recommend

About Joyk

Aggregate valuable and interesting links.

Joyk means Joy of geeK