Site Launch Exclusive: All the Juicy Details on AMD's Quirky Chipset Solutions f...

source link: https://angstronomics.substack.com/p/site-launch-exclusive-all-the-juicy?s=r

Go to the source link to view the article. You can view the picture content, updated content and better typesetting reading experience. If the link is broken, please click the button below to view the snapshot at that time.

Site Launch Exclusive: All the Juicy Details on AMD's Quirky Chipset Solutions for AM5!

Eastbridge? Westbridge?

As OEMs gear up for the announcement of their new AM5 motherboards at Computex Taipei 2022, more information begins to trickle out on a peculiar feature on these boards: their 600-series chipset.

In this premiere article celebrating the launch of Angstronomics, we will provide the full specifications, topologies and block diagrams of the AM5 platform and its chipsets, plus some additional bonus content on its history and development. Finally, after covering the what, we will also cover the why, detailing why this creative chipset solution was chosen and elaborate on the numerous advantages.

What is a Chipset Anyway?

Chipsets are companion devices on a computer motherboard that are paired with a main computing device such as a CPU and serve as a hub for Input / Output signals that interface with devices and connectors on the motherboard. This intermediate chip ‘bridged‘ the gap between I/O and processor, where the historical ‘Northbridge‘ handled high speed I/O to system memory and graphics cards, while a ‘Southbridge‘ handled low speed I/O to storage and networking. In this architecture, the CPU could be specifically designed to focus on compute and processing power, requiring only a single high speed link to the Northbridge. The chipset would focus on I/O distribution and management.

However, as technology advanced and system designs became increasingly integrated, the role of these chipsets diminished, where the main processor already has basically all the I/O interfaces onboard, from memory, PCI Express and storage devices, USB and even display outputs for integrated graphics. These System-on-Chips (SOCs) thus did away with discrete chipsets altogether.

In fact, AMD’s Ryzen line of client Desktop processors don’t even need a ‘chipset‘ as such to run, requiring only a tiny activator (Knoll) to operate. Branded as X300 and A300, these activators provide no additional I/O. Despite this, nearly all Desktop motherboards still contain a chipset, but in its modern iteration serve as I/O expansion hubs, not dissimilar to a multiport USB dongle. They allow one to plug in a greater quantity of devices, but all the data has to be funnelled through the equivalent bandwidth of a single port. This compromise is manageable so long as the attached devices are not all being used concurrently. The performance difference is negligible when you stay below the chipset uplink bandwidth to the processor. One can say that chipsets have been reduced to glorified PCIe mux switches.

With that out of the way, on to the fun stuff.

The AM5 Platform and Promontory 21

AMD’s upcoming client desktop platform for the DDR5 era was designed from the outset to rely entirely on chipset designed and made by a 3rd party supplier. This differs from the previous generation high-end X570 chipset from 2019 on the AM4 platform, where AMD repurposed their client I/O die chiplet repackaged for use as the aforementioned ‘glorified PCIe mux‘. The memory controllers, PHY and other unused functions just laid dormant in this chipset variant (Bixby). This resulted in a high-cost, high-power chipset solution that increased motherboard cost and sale price while also requiring an active cooling fan to cool the chipset on the first 2 years of X570 board designs. All this was done to get a chipset solution capable of PCIe Gen 4 linkspeed, which 3rd party manufacturers were not ready with at the time. Now that they are ready with PCIe4, AM5 returns to an exclusively 3rd party made solution, as was the case with the AM4 launch platform in 2016 with the original chipset made by ASMedia (Promontory), branded X370, B350, A320, X470, B450.

For AM5, there was also the intention to dual-source these chipsets from 2 different 3rd party suppliers, namely ASMedia and MediaTek. However, we note that more recent developments have exclusively focused on validation using ASMedia silicon, and are unsure when Mediatek will supply chipsets, if at all.

The AMD 600-series chipsets for AM5 are known as Promontory 21 (PROM21), and come in 3 configurations:

Low-end, presumably A620, with a single defeatured PROM21

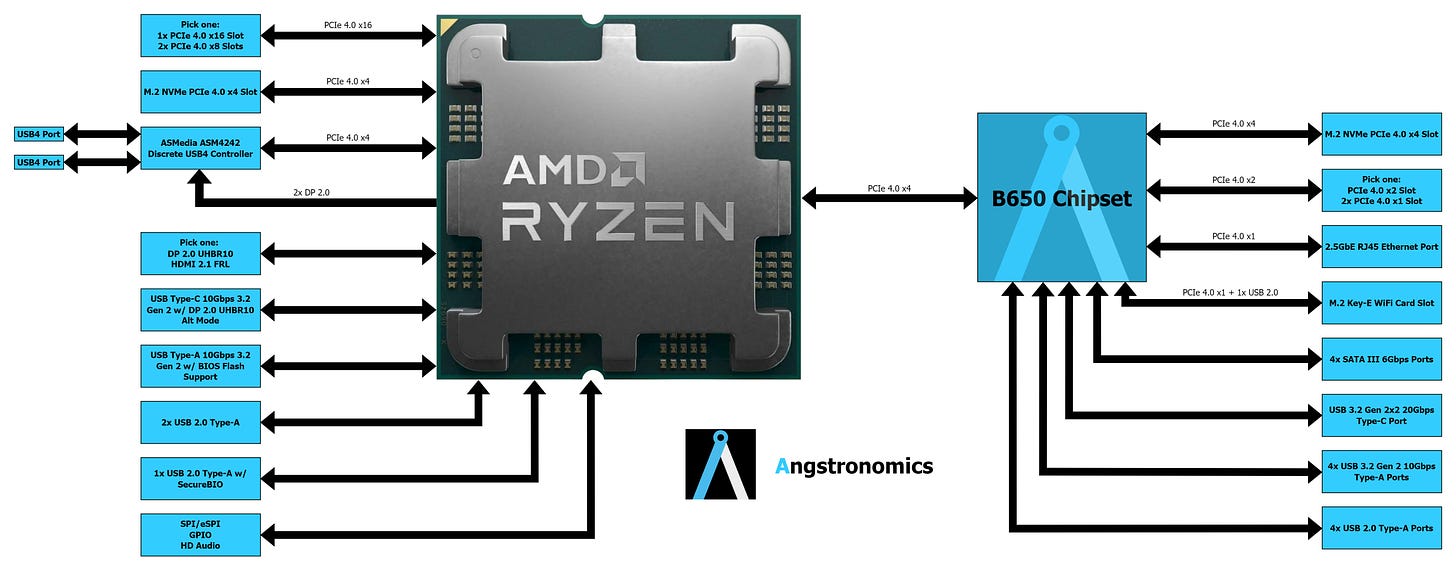

Mid-range, known as B650, with a single PROM21

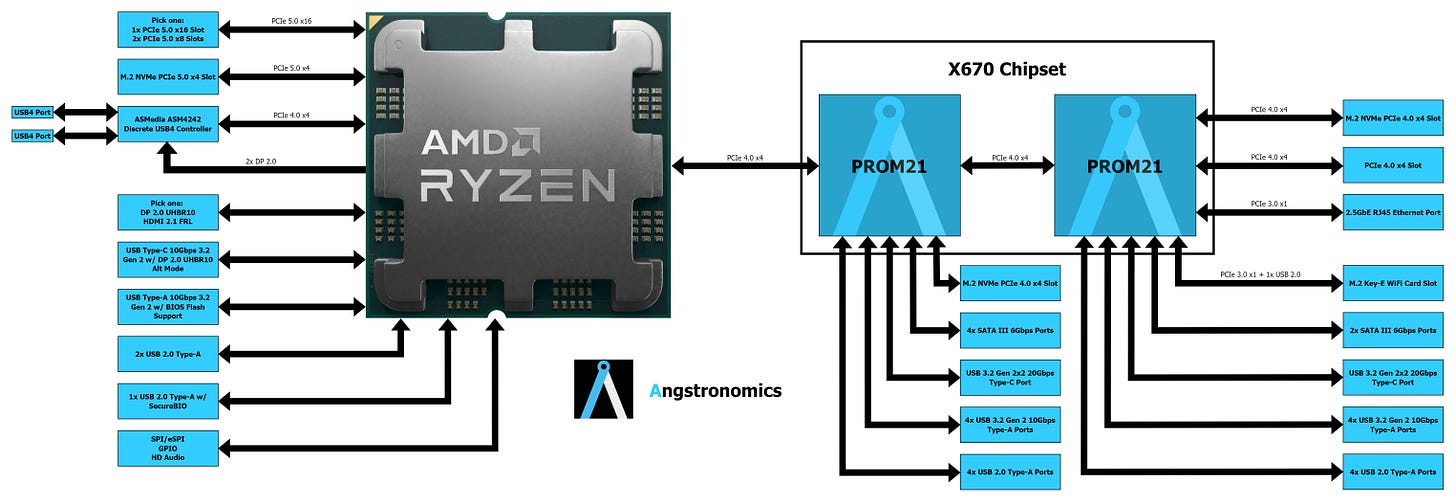

High-end, known as X670, with dual PROM21 chipsets on the motherboard

The A-class low-end chipset configuration will launch at a later date, appropriate when the lower-tier Rembrandt APUs launch on AM5.

The high-end X670 chipset is unique, featuring 2 separate PROM21 chipsets linked in a daisy-chained arrangement. The first chipset connects to the CPU, and the second chipset connects to the first chipset.

Here are the specifications of a single PROM21 chipset (B650):

19 x 19 mm FCBGA package

Maximum Power ~7W

One PCIe 4.0 x4 Uplink to host

Two PCIe 4.0 x4 downlink controllers (Total 8 Lanes)

Four PCIe 3.0 x1 / SATAIII 6 Gbps flexible ports (4L PCIe or 2L PCIe + 2x SATA or 4x SATA)

Six USB 3.2 Gen 2 10 Gbps ports (Two of the ports can be fused to form one USB 3.2 Gen 2x2 20Gbps port, with four remaining 10Gbps USB ports)

Up to 6 additional USB 2.0 ports

For the A-class chipset, one PCIe 4.0 x4 downlink is disabled

For a typical motherboard with 4x SATA ports, B650 can support one PCIe 4.0 x4 M.2 NVMe SSD, while the A-class chipset supports none. The remaining PCIe 4.0 lanes are used for WiFi, 2.5G Ethernet and PCIe x1 expansion slots.

The X670 boards have their daisy-chained chipsets linked with PCIe 4.0 x4.

Thus, the specifications of a dual PROM21 daisy-chained board (X670) are as follows:

Two 19 x 19 mm FCBGA packages

Maximum Power ~7W x 2

One PCIe 4.0 x4 Uplink to host

Three PCIe 4.0 x4 downlink controllers (Total 12 Lanes)

Eight PCIe 3.0 x1 / SATAIII 6 Gbps flexible ports (4L PCIe + 4x SATA or 2L PCIe + 6x SATA)

Twelve USB 3.2 Gen 2 10 Gbps ports (Four of the ports can be fused to form Two USB 3.2 Gen 2x2 20Gbps ports, with eight remaining 10Gbps USB ports)

Up to 12 additional USB 2.0 ports

The WiFi and 2.5G Ethernet can be connected to the PCIe 3.0 lanes, freeing up all 12 lanes of PCIe 4.0 downlink for M.2 devices and PCIe slots.

Additionally, there is plenty of I/O directly from the CPU:

One PCIe x16 slot for graphics (or bifurcated to two x8 slots)

One PCIe x4 slot for M.2 NVMe SSD

One PCIe x4 link for discrete USB4 controller (Maple Ridge JHL8540 or ASMedia ASM4242) or M.2 NVMe SSD

One PCIe 4.0 x4 for chipset downlink

Three combo USB-C ports supporting USB3.2 Gen 2 10Gbps and DisplayPort 2.0 UHBR10 Alt Mode (each combo port can be split into discrete DP and USB 2.0 Type-A)

One additional dedicated display output (DP 2.0 UHBR10 or HDMI 2.1 Fixed Rate Link or eDP)

One USB 3.2 Gen 2 10Gbps port with BIOS flash capability

One USB 2.0 port with SecureBIO support for Windows Hello capability

SPI/eSPI, GPIO, HD Audio

“X670E“ branded motherboards will require the primary PCIe and M.2 slots to support PCIe 5.0 linkrate. The chipset itself is identical to X670.

With that, here are the I/O block diagrams for a typical configuration of B650 and X670E motherboard. These represent a maximum supported configuration, as lower cost and smaller form factor board designs may expose less I/O.

Why Daisy-Chained Chipsets are a Great Idea

This Daisy-Chained chipset solution drastically lowers design costs, since ASMedia only has to design and tapeout a single chipset, while still allowing AMD to offer multiple segments of increasing motherboard I/O expansion features. When restricted to designing only a single piece of silicon to span across multiple market segments, it is much more cost-effective to design for the mass market middle-end solution and double up for the high-end rather than designing a larger, more expensive die that fits the requirements of the top end and then disabling features for the mass market segments.

There are also two more intrinsic bonuses that come with placing 2 chipsets on the motherboard. They don’t have to be placed together in the same spot. In fact, it is advantageous to place the chipsets further away from each other. By doing so, the first chipset functions as a signal repeater for the daisy-chained chipset, eliminating the need for additional signal retimers to reach places on the motherboard further from the processor with high speed PCIe 4.0 signals, thus lowering cost. Lastly, splitting the high-end chipset apart also spreads out the heat generation sources, lowering heat density and allowing for deisgns with passive cooling of the chipset, eliminating the need for a fan that just adds cost and another point of failure.

What’s the Catch?

No such thing as a free lunch, and that applies here as well. A daisy-chained I/O system increases the complexity of the system, with higher chances of bandwidth contention and unoptimized installation of devices, not to mention adding a second point of failure. Daisy-chained solutions also have inherently higher risks when trying to split up the hardware through Virtualization, where port assignment starts to cause headaches with nested I/O hubs. While it might just all work out fine in the end, it certainly isn’t part of best practices to plug a USB hub into another USB hub and attach mission critical devices to that. Same applies here with this chipset situation, but you can use the ports directly from the processor for that.

AMD: Pushing the Multi-Chip Game

After reintroducing multi-chip processors with their original EPYC 7001 in 2017, AMD is now doing multi-chip solutions for something as seemingly innocuous as the chipset. The cost advantage for AMD and ASMedia has clearly been worth it for them to go ahead on this unique and quirky idea!

If you enjoyed this work, do Subscribe and engage with us! We will be back soon covering the upcoming Computex event with even more juicy facts!

Recommend

About Joyk

Aggregate valuable and interesting links.

Joyk means Joy of geeK