延时校准、脉冲测试一定要做的事儿!

source link: https://www.eefocus.com/component/525311

Go to the source link to view the article. You can view the picture content, updated content and better typesetting reading experience. If the link is broken, please click the button below to view the snapshot at that time.

延时校准、脉冲测试一定要做的事儿!-基础器件-与非网

进行双脉冲测试的主要目的是获得功率半导体的开关特性,可以说它伴随着功率器件从研发制造到应用的整个生命周期。基于双脉冲测试获得的器件开关波形可以做很多事情,包括:通过对开关过程的分析验证器件设计方案并提出改进方向、提取开关特征参数制作器件规格书、计算开关损耗和反向恢复损耗为电源热设计提供数据支撑、不同厂商器件开关特性的对比等。

测量延时的影响

被测信号在测量过程中会经历两次延时,不同信号所经历延时的差别会对测量结果造成一定的影响。一次延时是示波器模拟前端的延时,索性示波器不同通道间延时差别在 ps 级别,对于 ns 级别的 ns、us 级别的功率器件开关过程可以忽略不计。另一次是探头的延时,不同的探头直接的延时差别在 ns 级别,此时对于开关速度较快的器件就有明显的影响了,特别是对于近几年开始逐渐推广使用的 SiC 和 GaN 器件影响就更大了。

我们以 SiC MOSFET 开关过程测量为例来说明测量延时的影响。

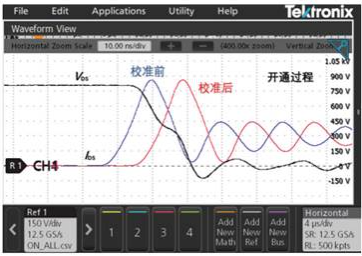

在下图中,蓝色波形为未对探头进行延时校准前获得的波形(校准前波形),红色波形为对探头进行延时校准后获得的波形(校准后波形)。

按照理论,在开通过程中,当 IDS 开始上升时,会在回路寄生电感上产生压降,这会使 VDS 有所下降,IDS 的上升与 VDS 的下降应该几乎在同一时刻开始的。而在校准前波形中,IDS 开始上升时,VDS 保持不变,在一段 5.5ns 延时后才开始下降。这一情况与理论明显不符合,可以推断此时 IDS 信号超前 VDS 信号。而在进行校准后,这一问题得到了解决。

版权声明:网站转载的所有的文章、图片、音频视频文件等资料的版权归版权所有人所有。如果本网所选内容的文章作者及编辑认为其作品不宜公开自由传播,或不应无偿使用,请及时通过电子邮件或电话通知我们,以迅速采取适当措施,避免给双方造成不必要的经济损失。侵权投诉

Recommend

About Joyk

Aggregate valuable and interesting links.

Joyk means Joy of geeK